计组笔记_chapter5

处理器的功能

- 指令控制

- 操作控制

- 时间控制

- 数据加工

- 中断处理

CPU=控制器+运算器+一堆寄存器

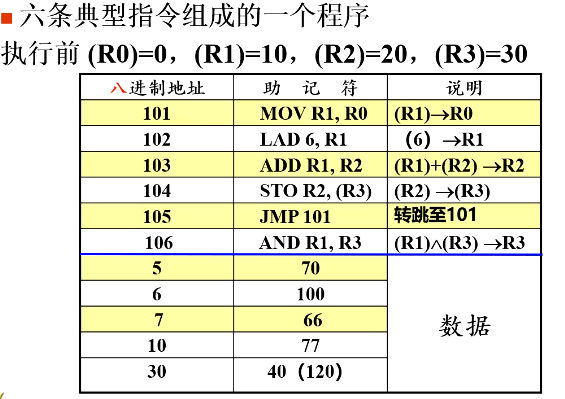

控制器

主要功能

- 从指令cache中取出一条指令,并指出下一条指令在指令cache中的位置

- 对指令进行译码或测试,产生相应的操作控制信号,以便启动规定的动作

- 指挥并控制CPU、内存和输入/输出设备之间数据流动的方向

运算器

组成:ALU,累加寄存器,数据缓冲寄存器DR,状态条件寄存器PSW

主要功能:

- 执行所有的算数和逻辑运算

- 并进行逻辑测试,如零值测试或两个值的比较

CPU中的主要寄存器(6种)

- 数据缓冲寄存器DR

用来暂时存放:- 向数据cache写入一个数据时,用DR暂存

- ALU计算结果

作用 - 作为ALU运算结果和通用寄存器之间信息传送中时间上的缓冲

- 补偿CPU和内存、外设之间在操作速度上的差别

- 指令寄存器IR(控制器内部)

用来保存当前正在执行的一条指令

指令寄存器中操作码字段的输出就是指令译码器的输入

操作码经过译码器译码之后,。。。 - 程序计数器PC(控制器内部)

也称指令计数器,来确定下一条指令的地址

在程序开始执行之前,将程序的第一条指令所在的内存单元送入PC

执行完之后会自加 - 地址寄存器AR

用来保存当前处理器所访问的数据cache - 通用寄存器R0~R3(一般举例子说是4个)

在ALU执行运算时,为其提供一个暂存数据的工作区

累加寄存器暂时存放ALU计算结果 - 状态条件寄存器PSW(ALU内部)

保存进位标志C,溢出标志O,是否为0Z,结果为负N等等

就是存汇编语言中标志位的那个。

操作控制器和时序产生器

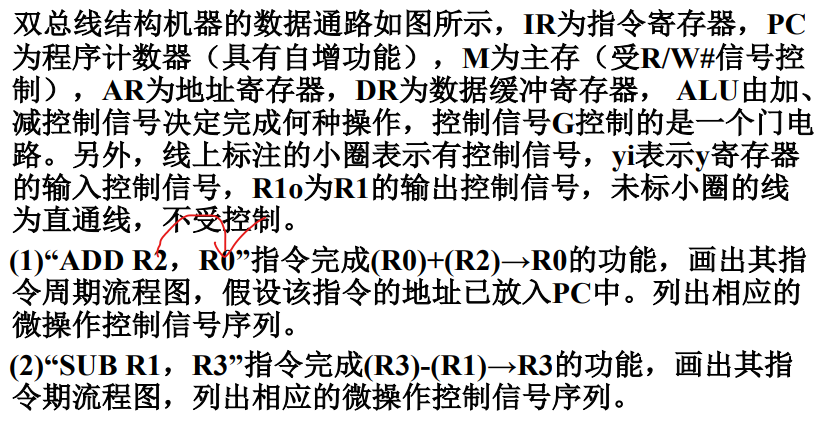

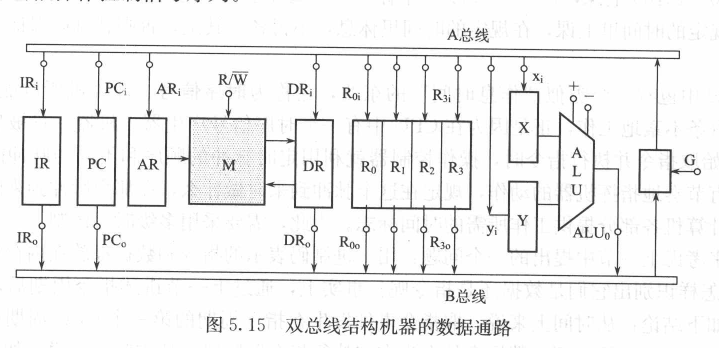

数据通路

操作控制器

功能:

根据设计方法的不同分类:

- 时序逻辑型 硬布线控制器(RISC也是)

- 存储逻辑性 微程序控制器(CISC也是)

时序产生器

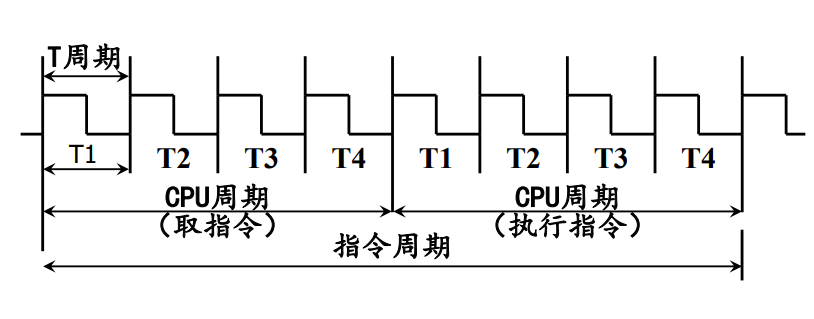

指令周期

基本概念

- 指令周期:取指令、分析指令、执行指令的time

由于各种指令的操作功能不同,各种指令的指令周期长度是不同的。

指令周期通常包含若干个CPU周期 - CPU周期,也称机器周期

内存中读取一个指令字的最短time

可以分成若干个时钟周期 - 时钟周期

处理操作的最基本的单位,也成为节拍脉冲/T周期

时钟周期是最基本的周期单位

如图

↑图中,分析指令过程被包含在执行指令过程中。时钟周期是最小单位,若干时钟周期组成CPU周期,若干CPU周期组成指令周期。

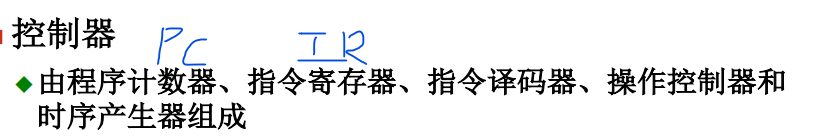

程序示例

Intel 汇编语言的指令与 AT&T 的指令操作数的方向上正好相反:在 Intel 语法中,第一个操作数是目的操作数,第二个操作数源操作数。而在 AT&T 中,第一个数是源操作数,第二个数是目的操作数。

这个程序示例里面是AT&T

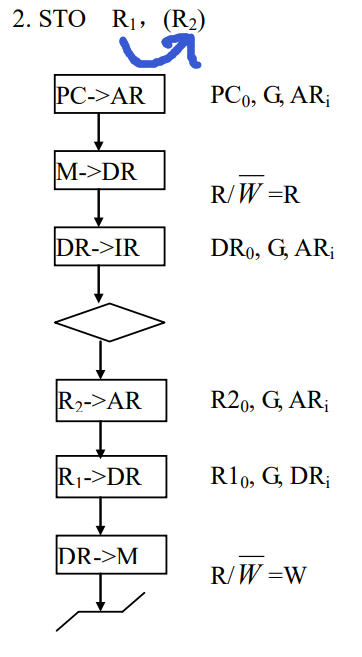

STO为写数指令

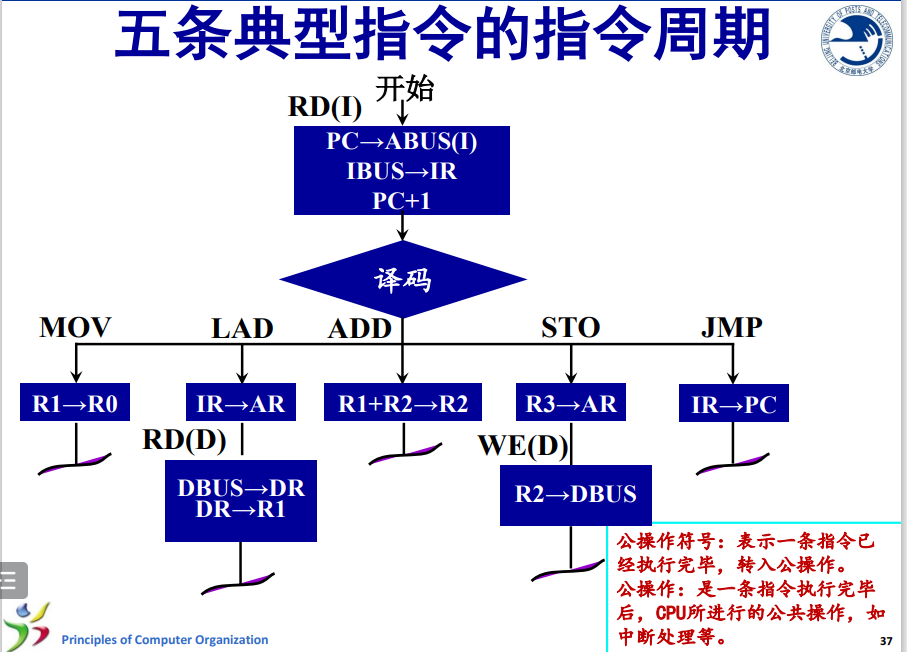

凡是RR型指令,都是2个CPU周期,RS型指令,都是3个COU周期。

每条指令的取指令阶段都是一样的,花费一个CPU周期,具体步骤是

- 根据PC的之(将要执行的指令的地址)从内存中取出指令,送到IR

- 取完之后PC就++

- 分离操作码和操作数,对指令进行译码

RS型指令多一个CPU周期的原因是需要送操作数地址。

特别的,JMP指令是无条件的转移指令,相当于是把某个立即数送到寄存器PC,并没有访问memory,所以还是2周期。

最后,检查有无中断的操作也是每条指令都要进行的操作。

方框图

- 方框:代表一个CPU周期,方框中的内容表示数据通路的操作或某种控制操作

- 菱形:通常用来表示某种判别或测试,在时间上依附于紧接它的前面一个方框的CPU周期,不单独占用一个CPU周期

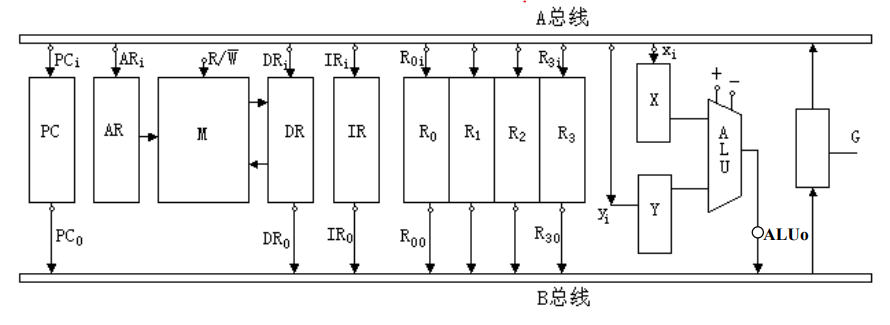

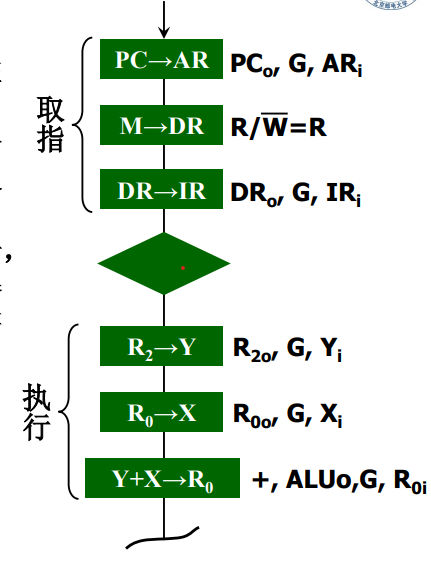

例子

答案

(1):

(2):

指令周期参考信号图

STO指令:

5.3时序产生器和控制方式

基本概念

时序 Timing

计算机以时序信号为基准完成协调动作

控制器分类:

- 硬布线控制器

时序信号一般采用主状态周期-节拍电位-节拍脉冲三级体制。节拍电位的时间=CPU周期的时间 - 微程序控制器

时序信号比较简单。一般采用节拍电位-节拍脉冲二级体制

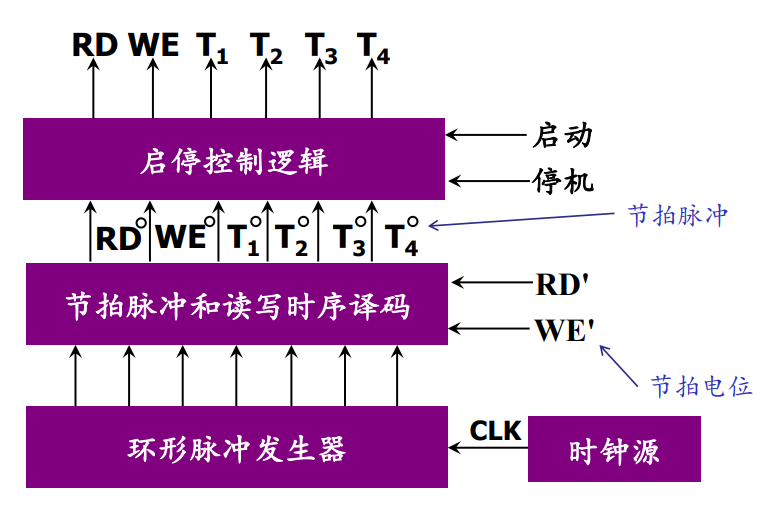

微程序控制器中时序信号产生器的组成:

- 时钟源

- 环形脉冲发生器

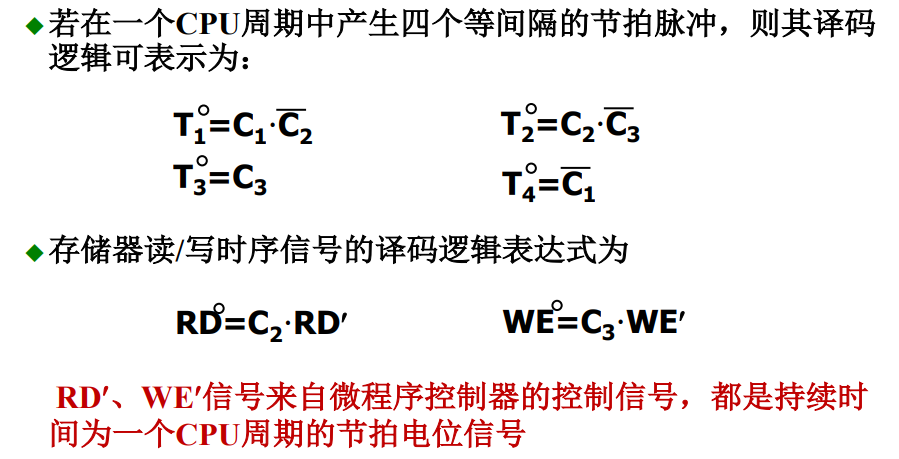

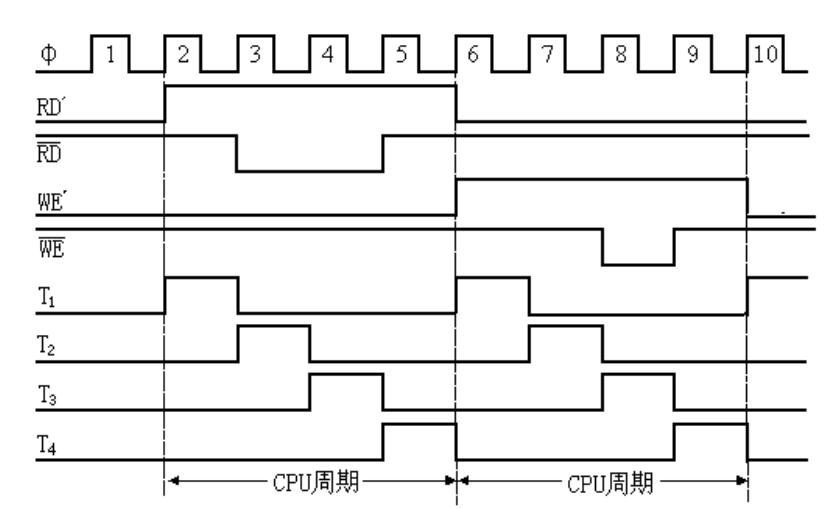

- 节拍脉冲和读/写时序的译码

- 启停控制逻辑

框图:

时钟源

环形脉冲发生器

- 产生一组有序的间隔相等或不等的脉冲序列,以便通过译码电路来产生最后所需的节拍脉冲

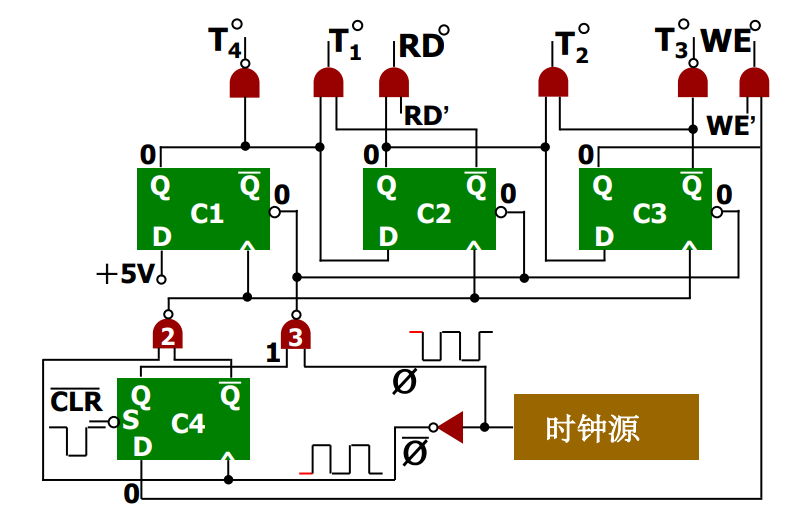

- 为了在节拍脉冲上不带干扰毛刺,环形脉冲发生器通常采用循环移位寄存器形式

节拍脉冲和读写时序的译码

译码逻辑:

一种环形脉冲发生器:

关于D触发器:左边的SD端是清零端,右边的RD端是预置端(置1)()二者都是低电平有效。

分析得,上图的电路状态是一个循环。

C1,C2,C3–>000->100->110->111->000

节拍电位与节拍脉冲时序关系图

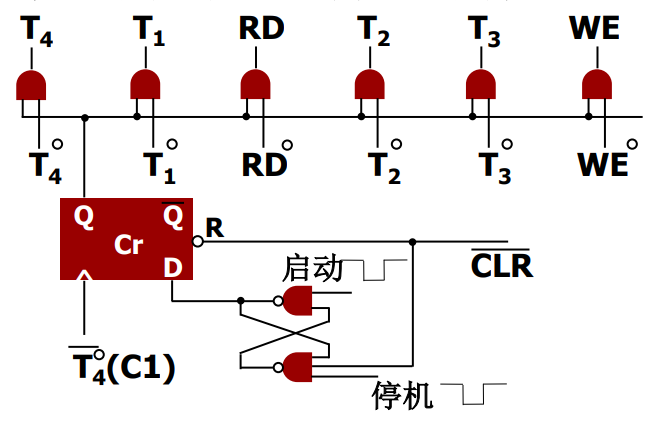

启停控制逻辑

启停控制逻辑

u机器一旦接通电源,就会自动产生原始的节拍脉冲信号T1°-T4°。但只有发出启动信号后,才允许时序产生器发出CPU工作所需的完整节拍脉冲

启动信号保证产生完整的CPU周期信号

启停控制逻辑

当触发器Cr的Q端为“1”时,原始节拍脉冲和读写信号通过门电路发送出去,变成CPU真正需要的节拍脉冲信号和读写时序,反之,就关闭时序产生器.

T4信号取反做时钟信号的原因:

保证时序信号以T1,T2,T3,T4的顺序输出。

控制方式

同步控制方式

Def:在任何情况下,各指令在执行时所需的机器周期数和时钟周期数是固定的

实现方案:

- 采用完全统一的机器周期执行不同的指令。简单指令会导致时间浪费

- 采用不定长机器周期,复杂指令采取延长机器周期的方法

- 中央控制与局部控制结合,上面俩结合

异步控制方式

- 每条指令,操作按需占用时间

- 不采用统一的时序信号,而是根据指令或者部件的具体情况而定。“应答”方式,没有时间上的浪费,但控制比较复杂.

联合控制方式

同步和异步相结合

- 大部分操作序列安排在固定的机器周期中,对某些时间难以确定的操作则采用“应答”信号作为本次操作的结束

- 机器周期的节拍脉冲数是固定的,但是各条指令的机器周期数不固定

微程序控制器

微程序设计技术是利用软件方法来设计硬件的一门技术

微程序控制器与硬布线控制器相比较,具有规整性、灵活性、可维护性等一系列优点

基本思想

- 用多条微指令(即:一个微程序)解释每条指令的执行过程。全部的微程序有机地组合在一起,存储在控制存储器(只读存储器)中。

- 当机器运行时,一条一条地读出这些微指令,从而产生全机所需要的各种操作控制信号,使相应的部件执行特定的操作

微命令和微操作

计算机的构成

- 控制部件–控制器

- 执行部件–运算器、存储器、外围设备

微命令-控制部件通过控制线向执行部件发出各种控制命令(即:控制信号)

微操作-执行部件接受微命令后所进行的特定操作

反馈信息

通常执行部件使用反馈线向控制部件报告操作情况,控制部件则根据执行部件的“状态”发出新的微命令。

分类:

- 相容性操作:同时或在同一个CPU周期内可以并行执行的微操作

- 相斥性操作:不能同时或不能在同一个CPU周期内并行执行的微操作

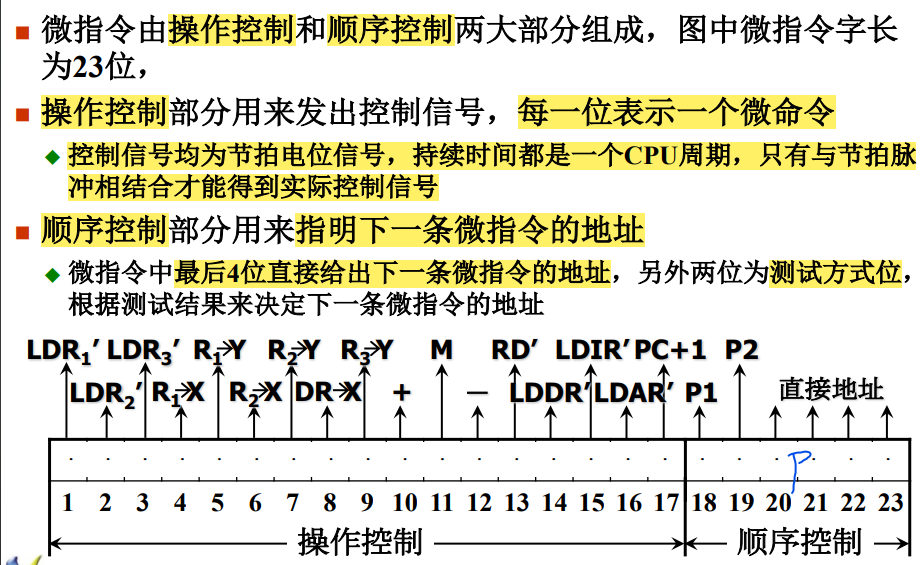

微指令

- 在机器的一个CPU周期中,一组实现一定操作功能的微命令的组合,构成一条微指令

或者说 - 用一条微指令对应一条机器指令的一个执行步骤

- 微指令需要具备的2个功能

- 供一条机器指令的一个执行步骤所需要的控制信号,以实现该执行步骤的操作功能

- 提供读出下一条待用微指令的地址,以便自动有序地读出每一条微指令,解决机器指令执行步骤之间的正确的接续关系

微指令基本格式

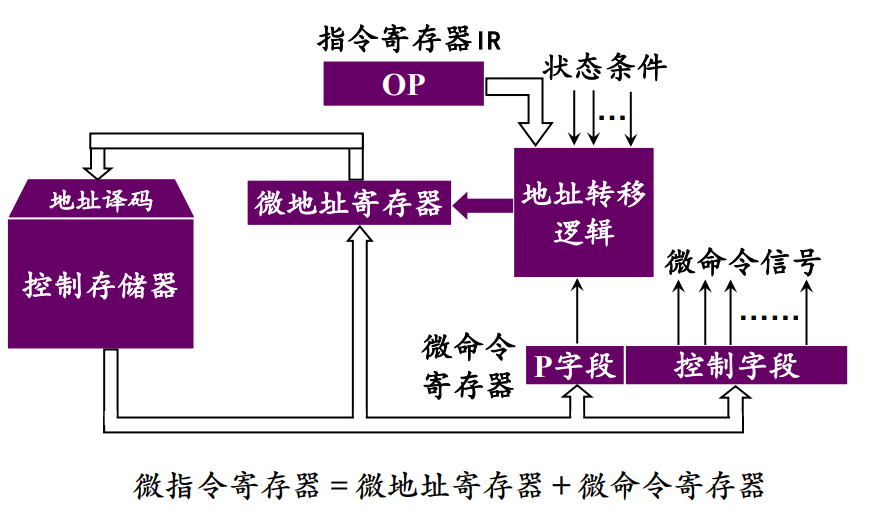

微程序控制器

- 控制存储器

- 微指令寄存器

- 微地址寄存器

- 微命令寄存器

- 地址转移逻辑

原理框图:

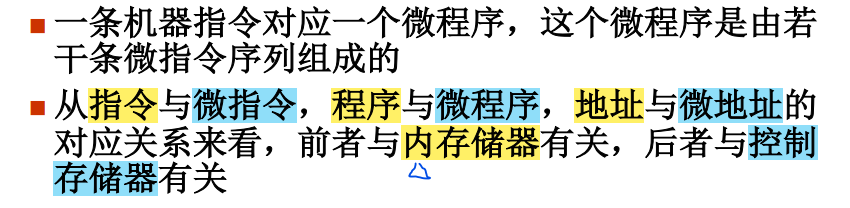

微程序的特点

一条机器指令是若干条微指令组成的序列来实现的

一条机器指令对应着一段微程序,而微程序的总和便可实现整个的指令系统

微程序设计可以很容易地在不同的微体系结构上实现相同的

以十进制加法指令操作码为地址,去查微地址映射部件得到微程序在控制存储器中的地址,就可以调出所需要的微程序(如上图中微程序地址为1010)

微地址映射部件是用ROM实现的,地址输入为指令寄存器IR的操作码,输出为该指令对应的微程序段的入口地址

微程序举例

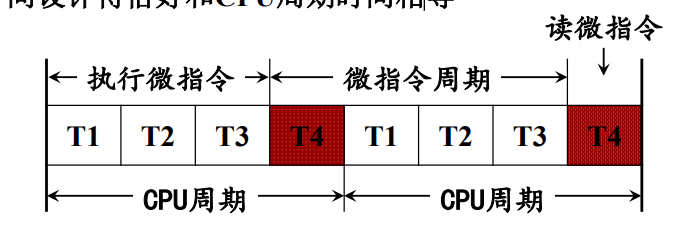

微指令周期与CPU周期的关系

微指令周期 = 读出微指令的时间 + 执行该条微指令的时间

为了保证整个机器控制信号的同步,可以将一个微指令周期 时间设计得恰好和CPU周期时间相等

机器指令与微指令的关系

5.4微程序设计技术

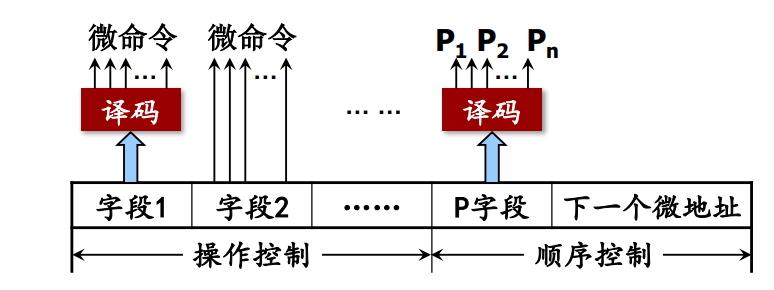

微命令编码

微指令操作控制字段的微命令表示方法可分为3类

- 直接表示法:操作控制字段中的每一位代表一个微命令

- 直接编码表示法:

把一组相斥性的微命令信号组成一个小组(即一个字段) ,然后通过小组(字段)译码器对每一个微命令信号进行译码 ,译码输出作为操作控制信号编码表示法使微指令字的长度大大缩短。但由于增加译码电路,微程序的执行速度稍稍减慢编码表示法使用较

- 混合表示法:见图

在微指令中还可附设一个常数字段

- 可作为操作数送入ALU运算

- 也可作为计数器初值用来控制微程序循环次数

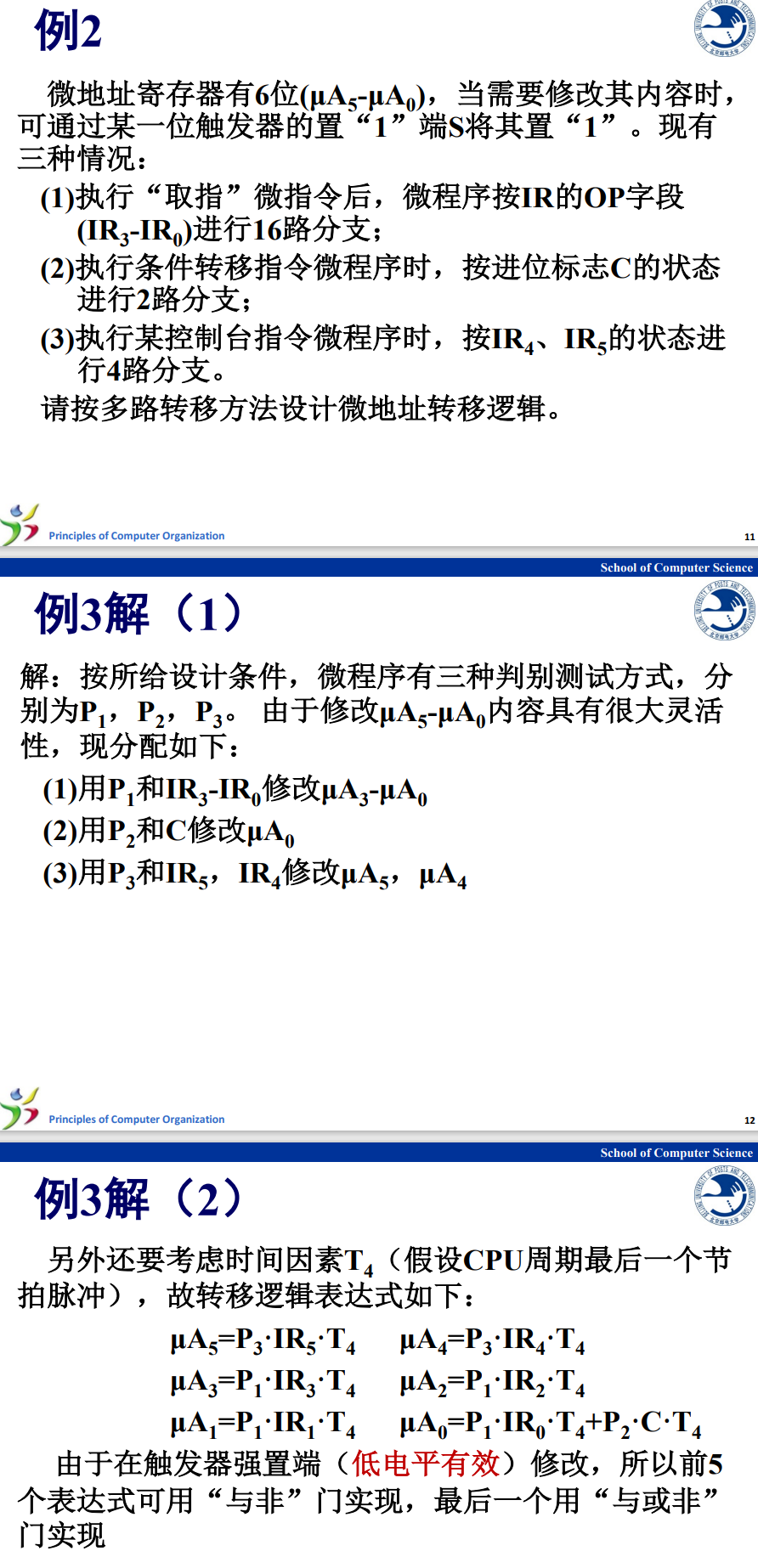

微地址的形成方法

产生后继微地址的方法

- 计数器方式(类似PC)

- 多路转移方式(跳转)

- 当微程序不产生分支时,后继微地址直接由微指令的顺序控制字段给出

- 当微程序出现分支时,有若干“候选”微地址可供选择:即按顺序控制字段P的“判别测试”和“状态条件”标志来选择其中一个微地址

- “状态条件”有n位标志,可实现微程序2n路转移,且涉及微地址寄存器的n位

- 由指令的操作码转换得到,典型方式为查表方式

微指令格式

- 水平型微指令

- 竖直型微指令

简单说,水平行比较长,上面那三种译码方式都是针对水平指令的,一次能定义并执行多个并行操作微命令。效率高,灵活性强,但基本别想凭肉眼看懂,因为每一位代表一个操作,然后每条指令就是微操作的组合(位的组合),然后最后写出来的微程序比较短,整体是个躺着的长方形(不恰当的比喻)。

竖直型指令就有点像经常见的指令了,有操作码,有源地址和目的地址。

每条指令完成的功能比较简单,所以最后写出来的微程序比较长,整体看就是个竖着的长方形。特别的,竖直型指令虽然完成的功能简单,这玩意儿执行时间还长。

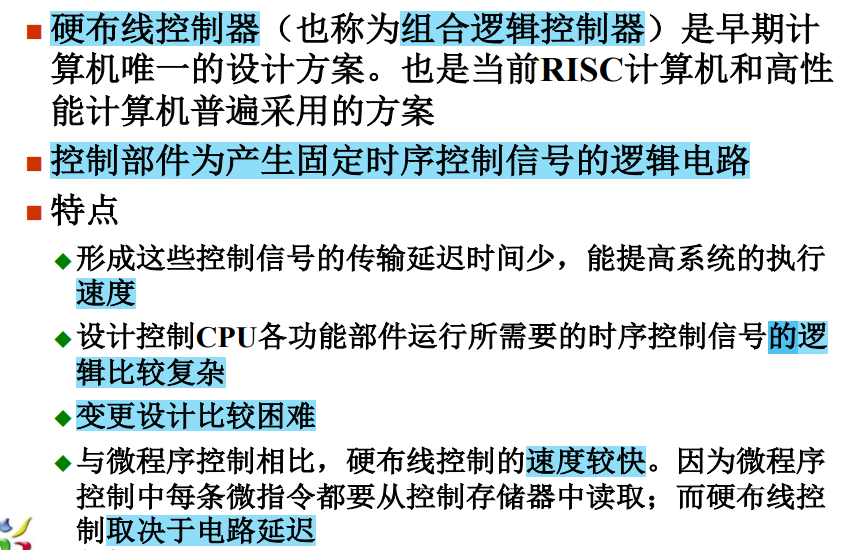

5.5硬连线控制器

基本概念:

硬连线控制器原理框图:

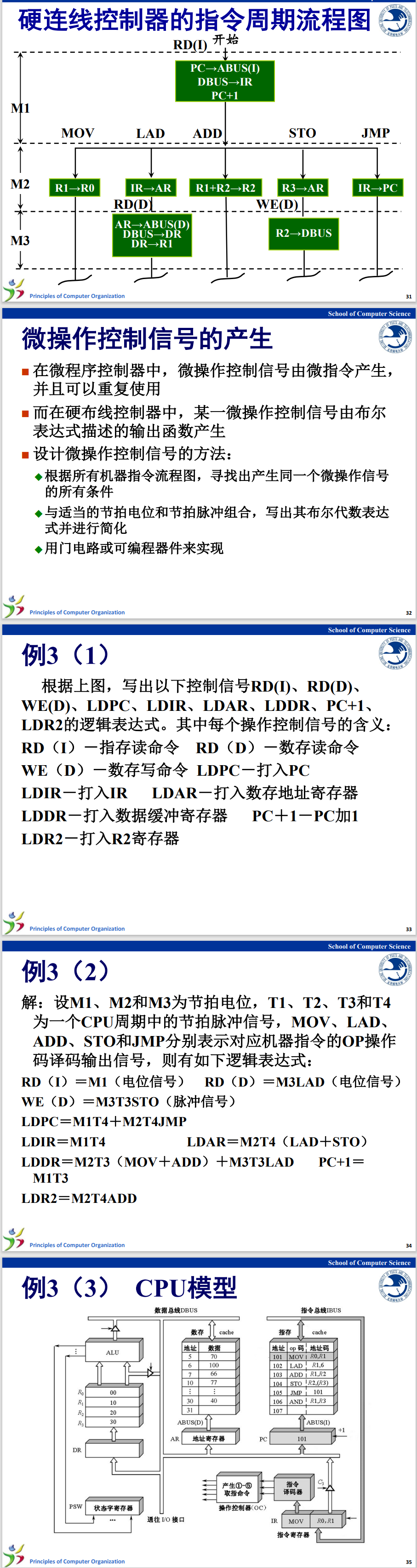

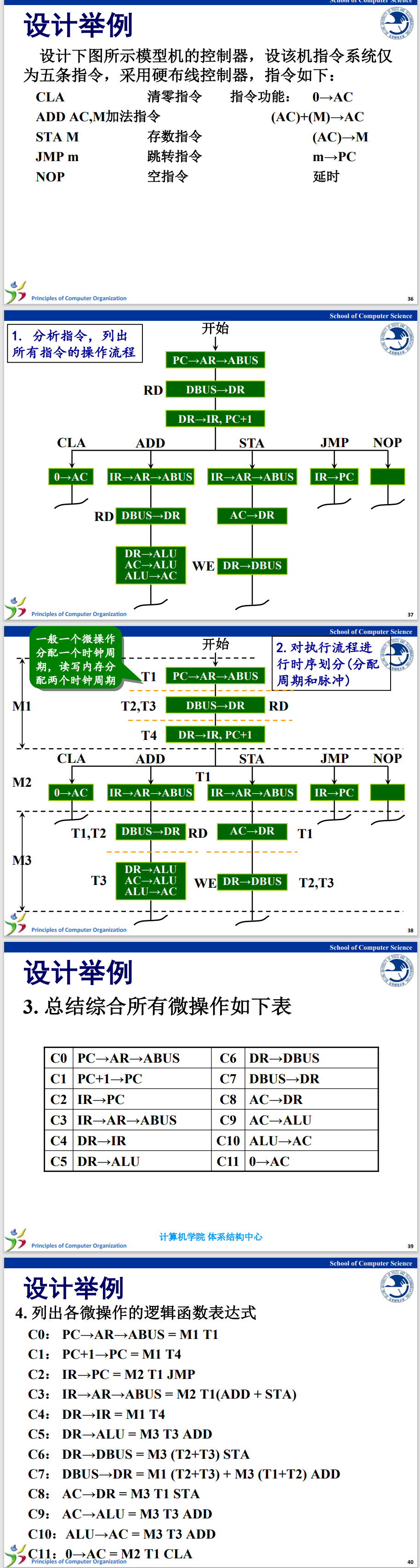

写出以下控制信号的逻辑表达式:

例子:

另一个举例:

这里需要注意的是T信号的划分:

一般一个微操作分配一个时钟周期,读写内存分配两个时钟周期

5.6流水CPU

流水方式CPU:指令部件、指令队列、执行部件

- 指令部件

- 指令队列:FIFO寄存器栈

- 执行部件:可以有多个采用流水线方式构成的算术逻辑部件构成,可以将定点运算部件和浮点运算部件分开

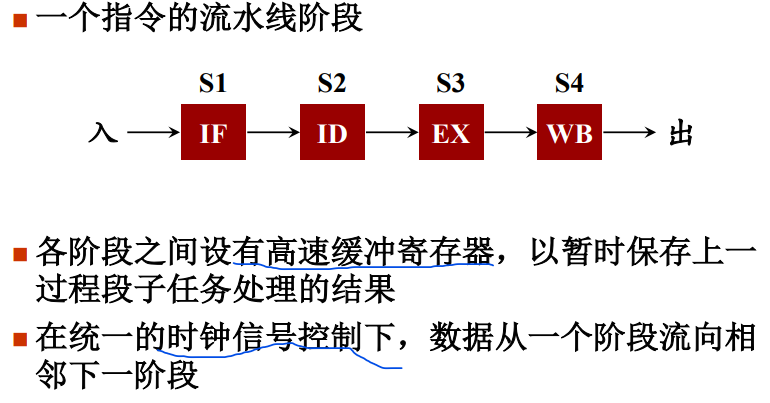

几个缩写的含义:

- IF(Instruction Fetch取指)

- ID(Instruction Decode指令译码)

- EX(Execution执行)

- WB(Write Back写回

4级指令流水线

几个概念:

线性流水线的时钟周期

$$

\tau=\max {\tau_i}+\tau_1=\tau+m+\tau_1;

$$